패터닝기술

| 기술명 | 나노임프린트 기반 나노홀 어레이 템플릿 제조기술 | ||

|---|---|---|---|

| 요약 | ㆍ 대면적의 Nano scale structure 구현을 위해서는 E-beam lithography 방식으로는 비용적인 측면에서 한계가 존재함. 그 대안으로 Nanoimprint lithography 방식을 통한 Wafer level의 SiO2 nano hole template을 구현한 결과임. | ||

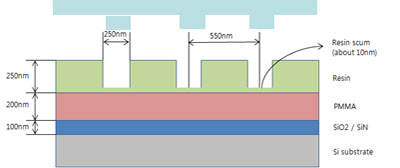

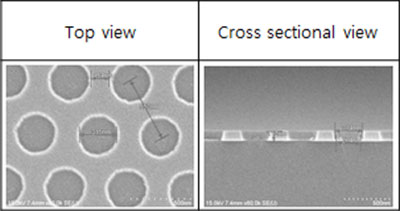

| 결과 | ㆍ Hole size : 300nm ㆍ Pitch : 550nm ㆍ Template thickness : 100nm ㆍ Sidewall angle : 108.5º ㆍ Substrate : 2inch Si |

||

| 사진 | ㆍ Layer structure |

||

| 기술적가치 | ㆍ Nano structure를 wafer level의 대면적에서 구현 가능하다는 점에서 cost down 효과를 얻을 수 있고, shape, size, pitch를 다변화하고, wafer 구경 대형화를 도모하여 가치를 더욱 증대시킬 수 있음. | ||

| 활동분야 | ㆍ Nanorod Epitaxial growth시 growth mask 로 활용 ㆍ Nano hole array pattern 제작을 위한 etch mask로 활용 ㆍ 광소자 표면 texturing을 위한 template로 활용 |

||

| 기술관련문의 | ㆍ 공정서비스지원실 이근우 책임 (031-546-6215, keunwoo.lee@kanc.re.kr) | ||